wallboston

Dabbler

- Joined

- Nov 20, 2022

- Messages

- 12

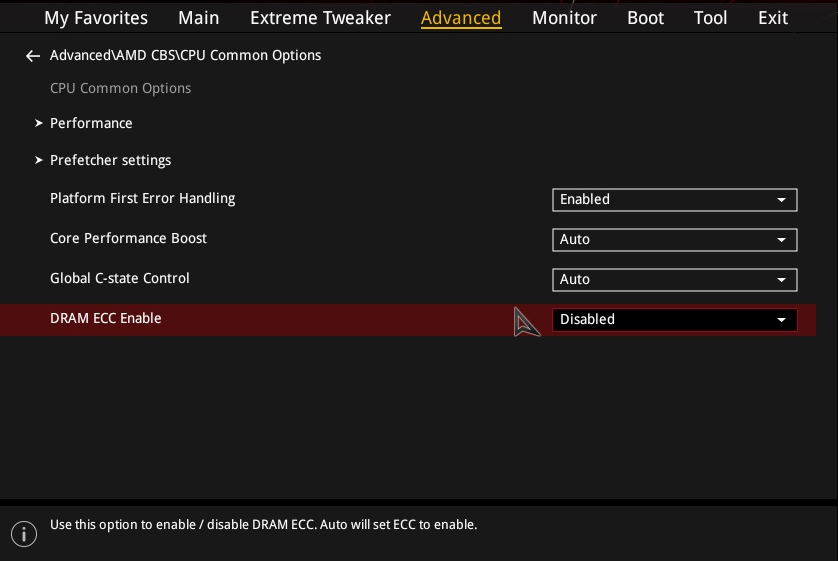

I have seen one other post from June 2020 address this issue but the resolution doesn't seem to apply to my problem. I just built my first TrueNAS system with the components below. I have run three different tests and none confirm that ECC is actually working. The motherboard BIOS manual page 73 says BIOS should display an "ECC Support" option that can be enabled/disabled. ECC Support is not being displayed in either BIOS version 1.6 or 1.8, the latest BIOS. Supermicro support claims the manual is out of date, that "ECC Support" is no longer displayed in the BIOS, but ECC is enabled by default. However, the three tests I ran all show ECC capability but none confirm that ECC is actually working. The most explicit test was PassMark MemTest86 Pro v10.1 which supports ECC injection for this CPU. That test shows no ECC errors being caught and corrected each time an error is injected by the test; injection is occurring but no correction. A screenshot of intermediate test results and an explanation from PassMark are also shown below.

Does anyone have this motherboard with "ECC Support" showing in the BIOS displayed under Advanced/Chipset Configuration/System Agent (SA) Configuration/Memory Configuration/ECC Support? Does anyone know if this option is supposed to appear in BIOS v1.8? I suspect I have a motherboard or BIOS issue preventing ECC operation but Supermicro isn't yet convinced. Does anyone have any other explanation for ECC not working with these components?

Selected System Components

Motherboard: Supermicro X11SCL-IF

CPU: Intel Xeon E-2234

RAM: Samsung 64GB (32x2) DDR4 2666

BIOS: v1.6 and v1.8 (I tested both)

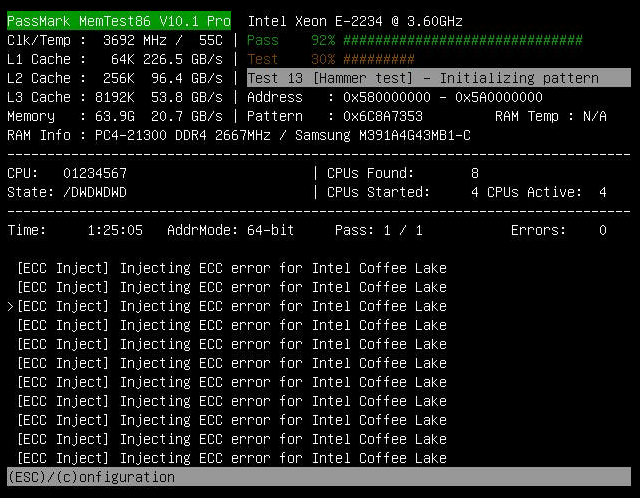

PassMark MemTest86 Pro Test Results and Explanation

Test results:

ECC injection explanation from PassMark:

“If ECC errors were successfully injected and detected by the system, the user shall see an [ECC Inject] message followed by an [ECC Errors Detected] message. If [ECC Errors Detected] message does not appear, it is highly likely the ECC injection is locked or disabled by BIOS.”

Note that the [ECC Errors Detected] message would appear immediately after and under each [ECC Inject] message in the screenshot above. No errors are being detected, hence ECC detection is not functioning.

Community thoughts, anyone? Thank you!

Does anyone have this motherboard with "ECC Support" showing in the BIOS displayed under Advanced/Chipset Configuration/System Agent (SA) Configuration/Memory Configuration/ECC Support? Does anyone know if this option is supposed to appear in BIOS v1.8? I suspect I have a motherboard or BIOS issue preventing ECC operation but Supermicro isn't yet convinced. Does anyone have any other explanation for ECC not working with these components?

Selected System Components

Motherboard: Supermicro X11SCL-IF

CPU: Intel Xeon E-2234

RAM: Samsung 64GB (32x2) DDR4 2666

BIOS: v1.6 and v1.8 (I tested both)

PassMark MemTest86 Pro Test Results and Explanation

Test results:

ECC injection explanation from PassMark:

“If ECC errors were successfully injected and detected by the system, the user shall see an [ECC Inject] message followed by an [ECC Errors Detected] message. If [ECC Errors Detected] message does not appear, it is highly likely the ECC injection is locked or disabled by BIOS.”

Note that the [ECC Errors Detected] message would appear immediately after and under each [ECC Inject] message in the screenshot above. No errors are being detected, hence ECC detection is not functioning.

Community thoughts, anyone? Thank you!